デジタルフロントエンド開発力強化ついてのご案内

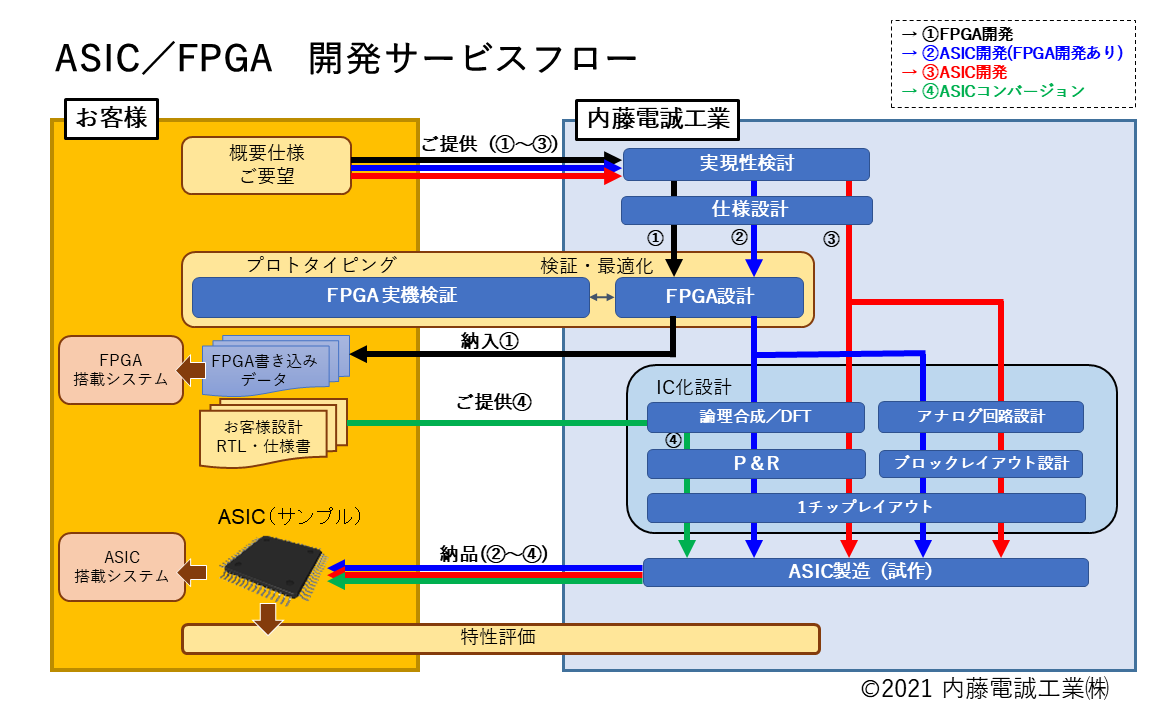

ターンキー開発におけるデジタルフロントエンドの開発力を強化しました。

従来のアナログ技術をベースとしたカスタムIC開発サービスに加え、より高度なデジタル機能を含むカスタムASIC開発サービスを提供致します。

併せて、FPGA開発サービスも開始します。

アナログ領域・デジタル領域の双方に精通するエンジニアチームが、カスタムASICやFPGAの開発を通して、お客様の様々な課題を解決します。

カスタムASIC開発サービスの特徴

・アナログ・デジタル両分野の経験豊富なエンジニアチームが、実現性検討~開発仕様提案を行います。お客様にヒアリングした内容からの仕様化も可能です。

・必要に応じてFPGAによるプロトタイピングを導入可能です。

・アナログ・ミックスドシグナルの豊富な経験も活かして、小型化・低コスト・省電力・拡張性・量産性などに配慮した、付加価値の高いソリューションを提供します。

・開発から量産供給までの「ターンキーサービス」の提供が可能です。

・お客様にて開発されたFPGAをカスタムASIC化する「ASICコンバージョンサービス」も承ります。既存のRTLをLSI用に最適化し、チップサイズ最小化やテスタビリティ確保などにより、カスタムASIC化のメリットを最大化します。

FPGA開発サービスの特徴

・ASIC開発におけるFPGAプロトタイピングで経験を積んだベテランエンジニアが担当します。

・コスト等の条件制約が厳しいASIC開発で培ったスキルにより、最適なFPGAデバイス選択と、そのポテンシャルを最大限に引き出すソリューションを提供します。

・将来のカスタムASIC化を想定した設計で、後のASICコンバージョンの際も迅速化・効果の最大化が期待できます。

・お客様とのヒアリングベースでの仕様提案も可能です。

・内藤電誠工業が得意とするアナログ回路も含めたFPGA評価ボードを提案します。

・お客様の詳細評価に基づく改良設計も承ります。

・対応FPGAデバイス

Xilinx, Intel(Altera) 等 お客様のご要望に合わせ対応します。

★開発可能技術領域

・デジタル信号処理回路 各種フィルタ/複素信号処理

・各種 ロジックI/F (I2C,SPI,I2S,UART等)

・EEPROM/RAM等のメモリー応用回路

など

ご質問、お問合せはこちらまで

お問い合わせ contact | 内藤電誠工業株式会社 (ndk-grp.co.jp)